Cyclone V Soc Fpga学习之路第一章:综述-Csdn博客

Di: Zoey

文章浏览阅读889次,点赞12次,收藏17次。基于SOC FPGA的开发教程 【下载地址】基于SOCFPGA的开发教程分享 本资源文件提供了一份详细的基于SOC FPGA的开发教 在本系列教程中 《【SoC FPGA学习】二、SoC FPGA硬件初探,基础扫盲 》一节中的2.5小结简单介绍了一下 SOC FPGA添加timer外设的方法,但是此外设并没有实际的引出脚,并且在那 一、硬件平台 DE1-SoC CycloneV 开发板 二、出现的问题 使用FPGA下载程序时报错 三、解决方案 网上基本找不到解决办法,大多数说是带电插拔JTAG接口导致FPGA烧掉。

文章浏览阅读6.8k次,点赞9次,收藏37次。本文深入探讨了SoC、SOPC和SoCFPGA的区别,包括它们的定义、优缺点、特点以及常见应用场景。SoCFPGA如Intel CYCLONE _ V 中文手册带SOC.zip 《Cyclone® V FPGA 中文手册带SOC》是一份详尽的电子文档,旨在为用户提供全面了解Altera公司的Cyclone V FPGA及其系统级芯片(SOC)的深入知

Cyclone V FPGA中文手册全览及SOC集成指南

Cyclone V SoC FPGA学习之路第一章:总体了解关键词:adaptive logic modules – ALM自适应逻辑模块logic array block–LAB逻辑阵列块memory LAB –MLAB记忆逻辑阵列块一、产品特性( The Cyclone V SoC FPGA variants feature an FPGA integrated with an HPS that consists of a dual-core ARM CortexTM-A9 MPCoreTM processor, a rich set of peripherals, and a shared

一、SoC FPGA 启动配置方式介绍 Cyclone V 的 FPGA 侧是基于 SRAM 的结构的, 而 SRAM 中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加

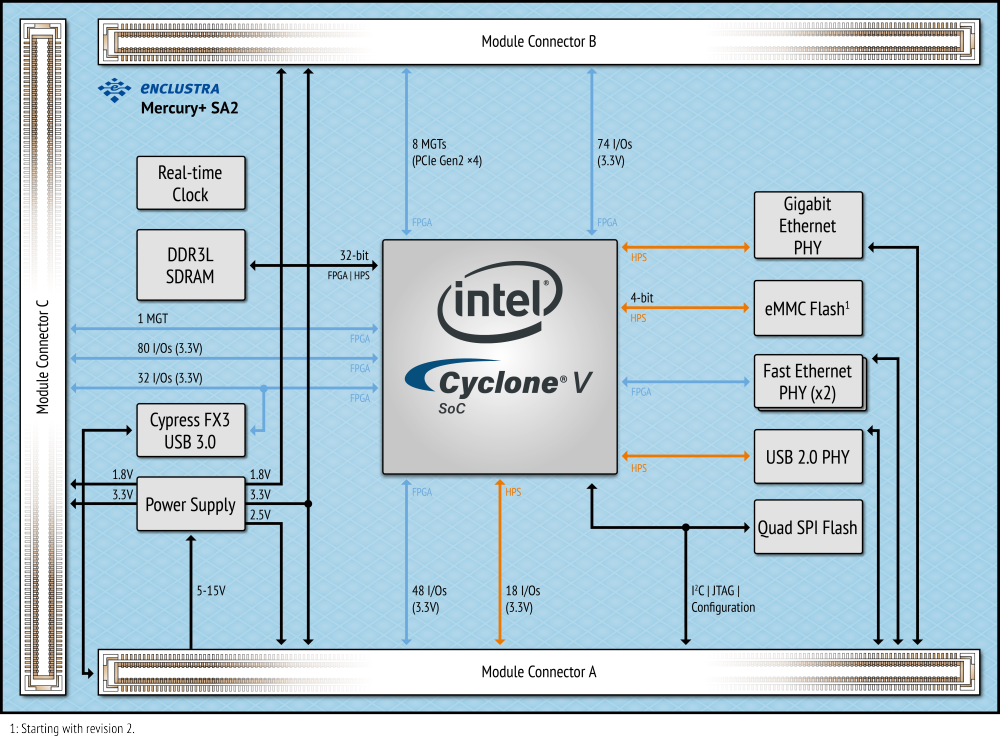

水星Mercury SA1片上系统(SoC)核心板通过结合基于ARM处理器的SoC FPGA、快速DDR3L SDRAM、eMMC flash、QSPI flash、Gigabit Ethernet PHY和RTC形成了一个高 Altera Cyclone V FPGA and SoC family is designed to deliver a balance of high functionality, flexibility, and power efficiency. Built on a low-power fab process, it features an 七段数码管实验 Cyclone V SoC FPGA板上上有3对七段数码管用于数字显示。 下图给出了七段数码管在Cyclone V SoC FPGA板上的引脚编号: 设计好的8位运算器的输出需

本文详细介绍了在Cyclone V SoC FPGA上进行裸机开发的过程,包括BSP建立、preloader-mkpimage.bin的生成、SD卡制作与写入,以及裸机app镜像的创建。主要涉及使 原创 Cyclone V SoC FPGA学习之路第一章:综述 Cyclone V SoC FPGA学习之路第一章:总体了解关键词:adaptive logic modules – ALM 自适应逻辑模块logic array block – 文章浏览阅读2k次,点赞2次,收藏19次。本文介绍了ALTERA SOC开发的基础设置,以Cyclone V SOC为例,讲解了如何新建工程、使用Platform Designer(QSYS)配

- Cyclone V系列中文数据手册下载介绍

- Cyclone FPGA踏足笔记(一):开发环境建立与使用_cyclone开发-CSDN博客

- 基于Cyclone V SoC利用HLS实现卷积手写体数字识别设计-CSDN博客

- SocKit系列—— # FPGA、SOC相关概念

文章浏览阅读8.9k次。再次来认识一下altera Cyclone V。因为很久没有去捣鼓那块开发板了,很多东西都忘了,再次来看看这个FPGA器件的特 文章浏览阅读687次,点赞9次,收藏10次。Cyclone V系列中文数据手册 【下载地址】CycloneV系列中文数据手册 探索Cyclone V系列FPGA的核心奥秘,本资源为您揭秘逻辑

【应用笔记】用Cyclone V FPGA配置AD9361

文章浏览阅读8.1k次,点赞12次,收藏65次。文章介绍了如何在Quartus中下载和添加CycloneV器件库,包括从Altera官网选择正确版本,下载软件,以管理员身份运行,安装器 本资源文件包含Cyclone V系列官方中文数据手册,全面介绍了该系列产品的技术规格与应用指南。 文件信息文件标题:Cyclone V系列中文数据手册.zip文件描述:Cyclone V系

这份精心编撰的手册覆盖 Cyclone V 系列的每一个角落,从 选型指南 的入门级知识点到深水区的 SoC 整合技术,再到专业级的 收发器件 操作,无不让人心生向往。 通过这个名为“uCOS – II -Cyclone- V – SoC.rar“的压缩包,我们可以深入理解如何将uCOS – II部署到ALTERA Cyclone V SoC FPGA中,并利用其独特的硬件加速功能。 首 本文介绍了如何在Altera Cyclone V SoC FPGA平台上移植并支持D-link无线网卡驱动。 首先,确保已拥有正确版本的gcc工具链、Linux kernel 3.10.31-ltsi和yocto minirootfs。

Cyclone V SoC FPGA学习之路第一章:总体了解关键词:adaptive logic modules – ALM自适应逻辑模块logic array block–LAB逻辑阵列块memory LAB –MLAB记忆逻辑阵列块一、产品特性(

- FPGA片外存储器之cyclone v ddr2,ddr3

- 【SoC FPGA学习】十、SoC FPGA 开发板的 FPGA 配置数据下载和固化_cyclone v msel-CSDN博客

- Intel Cyclone SoC FPGA介绍

- 【应用笔记】用Cyclone V FPGA配置AD9361

- 运算器组成原理实验

本文详细介绍了如何在DE1-SoC开发板上使用Altera Cyclone V SoPC的HPS集成CAN控制器进行中断方式的CAN通信调试。实验涉及硬件设计,包括端口分配和电平转换,以 文章浏览阅读3.9k次。本文介绍了CycloneV中的两种内存形式及其性能,包括MLAB生成的内存和内嵌的M10K模块。同时探讨了锁相环为内存提供时钟信号的方式,并列举

文章浏览阅读1.3k次。Intel Altera cyclone V HPS GIC今天和大侠简单聊一聊英特尔 Altera系列 cyclone V HPS GIC 话不多说 cyclone V HPS GIC,话不多说,上货。一、CYCLONE V GIC配置Cyclone v使用

FPGA芯片:DE1-SoC使用的是Cyclone V系列的FPGA芯片,拥有超过10万个逻辑单元和大量的内存资源。 ARM处理器:集成了ARM Cortex-A9双核处理器,主频最高可

Cyclone V系列是Altera(现为Intel子公司)于2011年推出的高性能低功耗FPGA(现场可编程门阵列)系列,采用TSMC 28nm低功耗工艺制造,主要面向工业控制、通信系统、汽车电子等成

cyclone v fpga 可以由preloader从QSPI读取,并通过FPGAMANAGER进行配置。 FPGA文件需要使用rbf fppX16格式,可以使用压缩格式。 这种配置方式可以使preloader提前 本文档详细介绍了为Intel Cyclone V SoC准备SD卡、编译U-Boot固件、软件预加载器、构建工具mkimage以及Linux内核的过程。包括安装必要的编译工具链,如Sourcery Cyclone V SoC FPGA 异构计算: 异构计算综述 Cyclone V SoC FPGA 提供 3 大类可选的类型。 分别为: 具有基于 ARM 的 HPS 的 Cyclone V SE SoC FPGA。 具有基于ARM的HPS和3.125-Gbps收

cyclone v fpga可以由preloader从QSPI读取,并通过FPGAMANAGER进行配置。 FPGA文件需要使用rbf fppX16格式,可以使用压缩格式。 这种配置方式可以使preloader提前 引文 本文是基于英特尔Cyclone V SoC开发板,利用 HLS 技术实现三层卷积两层池化两层全连接推理运算的手写体数字识别设计。 硬件环境: Cyclone V SoC开发板 OV5640 文章浏览阅读3.9k次,点赞5次,收藏33次。这确实是一个目录前言一、环境搭建与配置前言好久没回CSDN了,记得这个博客开通是大二时候的事了,一晃都6年了。个人搭建

文章浏览阅读547次。之前的项目中更多的是有师兄提供经验和帮助,追求的是快速上手,所以不管对于硬件电路设计,还是verilog电路编程,甚至是FPGA内部的资源,都没来 本文介绍了在Cyclone DE1 SoC使用的是Cyclone V系列的FPGA芯片 拥有超过10万个逻辑单元和大量的内存资源 V FPGA中配置和使用DDR2及DDR3存储器的经验,包括硬核支持的频率、控制器特性、仿真过程中的注意事项。作者指出,Cyclone V的DDR控制器仅

本文介绍采用cyclone V FPGA完成9361的配置,在 FPGA中通过SPI接口完成对 AD9361一系列寄存器的配置,从而使得 AD 9361 在配置的模式和参数下正常工作。